## World's First Copper-Free Silicon Wafers for Integrated Photonics

Create absorption-free photonic integrated circuits with copper-free silicon wafers engineered for ultra-low loss and reproducible wafer-scale photonic performance.

### Copper Contamination – The critical Barrier to Scalable Photonics

Even trace amounts of copper diffuse into dielectric PIC layers during wafer processing. In low loss photonic integrated circuits, this contamination creates absorption centers that create thermal drift and reduce Q-factors – **limitations fully overcome by our copper-free silicon wafers, enabling:**

- ✚ Ultra-low thermal drift and highly stable resonances

- ✚ Ultra-low optical loss and consistently high Q-factors

- ✚ Uniform device performance across full wafers

- ✚ Predictable, repeatable soliton formation in  $\text{Si}_3\text{N}_4$  microresonators

Suitable for high-performance microcombs, next-generation LiDAR, precision sensing platforms, communication systems and quantum photonic devices.

**Copper contamination destabilizes low loss integrated photonic circuits at scale.** As applications move from labs into commercial systems, this contamination can become a critical barrier to device performance.

### Our Patented Technology

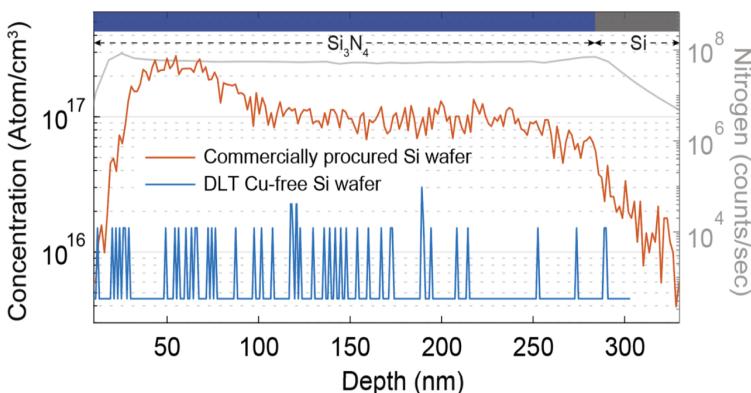

Figure 1: Cu depth profile in Si wafers.

Deeplight provides 100mm and 150mm silicon wafers engineered to prevent copper diffusion into photonic device layers. Instead of attempting to mitigate absorption-related degradation later in the process, we remove the root cause at the substrate level.

This results in a cleaner material platform that preserves optical purity through full wafer fabrication and packaging flows.

*No changes required to your photonic process.

No impact on foundry compatibility.*

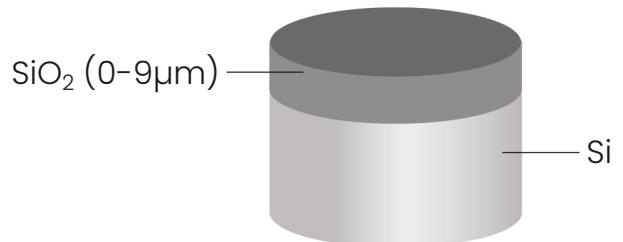

## Our Product Offering: Silicon Wafer with Thermal Oxide Film

|                              |                         |

|------------------------------|-------------------------|

| Size (Inch)                  | 4 / 6                   |

| Thermal Oxide thickness (nm) | 0 – 9000                |

| MOQ (pcs)                    | 10                      |

| Silicon wafer thickness      | 300 – 500 $\mu\text{m}$ |

### Undercladding wafer

Up to 9 $\mu\text{m}$  thermal oxide

### Case example: Deterministic Soliton Microcomb

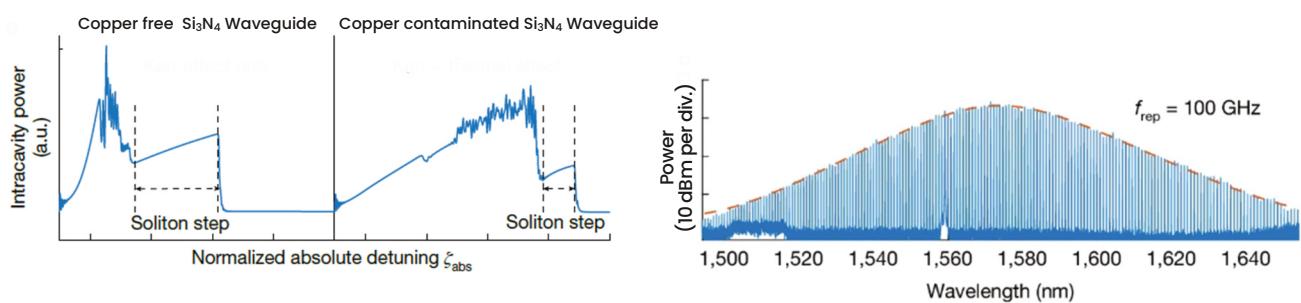

Deeplight copper-free wafers eliminate copper migration into photonic layers, removing a key source of optical absorption and thermal drift.

With this clean substrate foundation, Si<sub>3</sub>N<sub>4</sub> microresonators achieve stable and repeatable soliton formation, even at low repetition rates around 40 GHz where thermal sensitivity is very high.

This enables deterministic DKS generation without complex tuning schemes, unlocking reliable microcomb operation for next-generation coherent sensing, precision timing, and communications systems.

**Figure 2:** Effect of copper contamination on soliton step length (left); Single-soliton spectra from a Si<sub>3</sub>N<sub>4</sub> microresonator with FSRs of 100 GHz fabricated on copper-free Si wafers (right)